DOI: 10.2478/msp-2019-0065

## SiN/SiO<sub>2</sub> passivation stack of n-type silicon surface

A. EL AMRANI\*, R. SI-KADDOUR, M. MAOUDJ, C. NASRAOUI

Research Center in Semiconductor Technology for Energetic, 02 Bd. Frantz Fanon-Alger, BP N°140, Les 07 Merveilles, 16038, Algiers, Algeria

The  $SiN/SiO_2$  stack is widely used to passivate the surface of n-type monocrystalline silicon solar cells. In this work, we have undertaken a study to compare the stack layer obtained with  $SiO_2$  grown by both rapid thermal and chemical ways to passivate n-type monocrystalline silicon surface. By varying the plateau time and the plateau temperature of the rapid thermal oxidation, we determined the parameters to grow 10 nm thick oxide. Two-step nitric acid oxidation was used to grow 2 nm thick silicon oxide. Silicon nitride films with three refractive indices were used to produce the  $SiN/SiO_2$  stack. Regarding this parameter, the minority carrier lifetime measured by means of QSSPC revealed that the refractive index of 1.9 ensured the best passivation quality of silicon wafer surface. We also found that stacks with nitric acid oxidation showed definitely the best passivation quality. In addition to produce the most efficient passivation, this technique has the lowest thermal budget.

Keywords: silicon; passivation; silicon nitride; oxide

#### 1. Introduction

Minimization of surface recombination losses is an important issue for electrical characteristics improvement of a large variety of silicon-based microelectronic devices [1] and silicon-wafer-based solar cells [2]. Indeed, to enhance the efficiency of solar cells, recombination losses must be minimized [3]. Effective surface passivation of crystalline silicon has been performed using amorphous silicon [4], amorphous silicon carbide [5] and aluminum oxide [6]. Surface passivation is also achieved by amorphous hydrogenated silicon nitride (abbreviated SiN) [7–11]. Another passivating material is thermally grown silicon dioxide (SiO<sub>2</sub>). This material has been used in the most common methods for passivating a silicon surface, offering excellent interface characteristics, crucial for high efficiency silicon solar cells [12]. However, its high process temperature and high thermal budget are the major drawback. Rapid thermal oxidation (RTO) was demonstrated to provide sufficient passivation for solar cells [13] with a reduced thermal budget. Due to the use of halogen lamps, RTO systems can rapidly increase and decrease

the temperature. Within seconds, the temperature can rise from room temperature to 1000 °C. With this furnace, oxidation can be completed within minutes reducing the thermal budget. Another short oxidation process is so-called nitric acid oxidation of silicon (abbreviated NAOS). It is a wet and low temperature method, where the NAOS SiO<sub>2</sub> layer is formed within minutes in nitric acid (HNO<sub>3</sub>) bath as described in the literature [14–16].

For p-type solar cells, the PECVD silicon nitride is used as a surface passivation film. This material has been found not efficient for n-type silicon solar cells because of the positive surface charge which is the main origin of parasitic shunting in SiN passivated emitters. For this material, an improved front surface passivation and antireflection coating (ARC) consisting of a SiN/SiO<sub>2</sub> stack is a solution [17]. It has been demonstrated that this stack can stabilize the Si/SiO<sub>2</sub> interface, preventing significant degradation by air moisture [18, 19]. Also, SiN films contain a significant amount of hydrogen, therefore, when an annealing is performed, hydrogen diffuses from SiN towards the Si/SiO<sub>2</sub> interface where it forms Si-H bonds, significantly reducing the interface defect density [17]. Many surface passivation studies in the manufacture of silicon-based solar cells

<sup>\*</sup>E-mail: elamrani@msn.com

are performed for the growth of  $SiO_2$  on silicon substrate. In this work, the surface passivation quality of n-type monocrystalline silicon using  $SiN/SiO_2$  stack is investigated. Results of stacks made of  $SiO_2$  layers grown by RTO and NAOS have been evaluated and compared. Both layers formation are comparable in terms of process duration.

## 2. Experimental

#### 2.1. Sample preparation

The experiments were conducted on 4 inches  $\langle 1\ 0\ 0 \rangle$  n-type double side polished CZ-monocrystalline silicon wafers. Low resistivity (1  $\Omega \cdot$  cm to 3  $\Omega \cdot$  cm) and high resistivity (8  $\Omega \cdot$  cm to 12  $\Omega \cdot$  cm) wafers were used to measure the oxide thickness and to assess the passivation quality. The wafers were first cleaned using Piranha etch procedure.

#### 2.2. Materials used

The rapid thermal oxidations were performed with a single wafer in a rapid thermal process furnace from Allwin (Accu Thermo AW610). The chemical oxides (NAOS) were grown by immersion of wafers in chemical bath containing HNO<sub>3</sub>. SiN films were deposited in a direct-plasmaenhanced chemical vapor deposition (PECVD) operating at low frequency. A pure silane (SiH<sub>4</sub>) and pure ammonia (NH<sub>3</sub>) were used as process gases.

#### 2.3. Characterizations

The passivation quality was assessed using the quasi-steady-state photoconductance (QSSPC) technique. A Sinton WCT 120 station was used to measure the minority carrier lifetime ( $\tau_{eff}$ ) on symmetrically processed test wafers. The oxide and SiN thicknesses were measured with an ELX 02C (DRE GMBH) ellipsometer operating at laser light wavelength of 632.8 nm. This instrument is a computer controlled measuring equipment of very high precision. It is able to measure thin films between 0.1 nm and 600 nm with an accuracy of 0.1 nm under the following conditions: darkness and stable laser. The depth profile of hydrogen

concentration in the SiN film was measured by means of secondary ion mass spectroscopy (SIMS) CAMECA 4FE7.

## 3. Results and discussion

# 3.1. Rapid thermal oxidation (RTO) growth

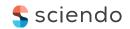

The objective was to determine RTO parameters leading to the optimal oxide thickness (around 10 nm) [20, 21]. Preliminary experiments have led us to keep a constant oxygen flow rate at its maximum value of 20 slm (standard liters per minute) and vary the plateau temperature ( $T_{max}$ ) between 900 °C and 950 °C. A typical RTO profile used is shown in Fig. 1.

Fig. 1. Typical RTO profile used.

#### 3.1.1. Oxide thickness uniformity

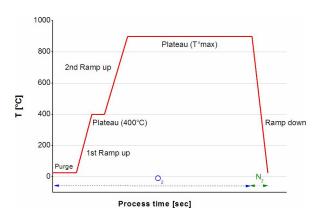

Fig. 2 shows the measured oxide thickness for each side of the same wafer as a function of oxygen flow rate at  $T_{max}$  of 900 °C. This figure provides information on side-to-side oxide thickness uniformity. The oxide grew uniformly on both sides of the wafer. The uniformity was about 6 %. The same applies to the uniformity on each side where the worst value calculated was 6 %.

#### 3.1.2. Plateau temperature $(T_{max})$

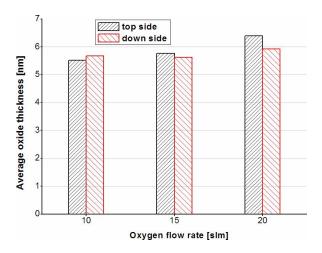

As shown in Fig. 3,  $SiO_2$  thickness increases from 5.5 nm to around 9 nm, when the temperature increases from 900 °C to 950 °C.

Fig. 2. Comparison of the oxide thickness at both sides of the wafer as a function of oxygen flow rate  $(T_{max} = 900 \, ^{\circ}\text{C})$ .

Fig. 3. Oxide thickness as a function of plateau temperature at 20 slm oxygen flow rate and plateau time of 135 s.

#### 3.1.3. Plateau time

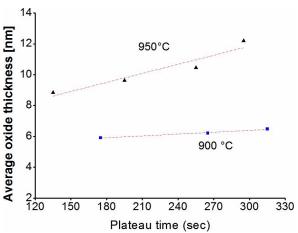

Fig. 4 shows the  $SiO_2$  thickness at 900 °C and 950 °C in dependence on the plateau time. For  $T_{max}$  of 900 °C, the oxide growth rate increases very slowly. If we take into account that the maximum plateau time is 315 s, the highest oxide thickness which can be reached at this temperature is then around 6 nm.

For temperature of 950 °C, the growth rate is 2.52 nm/min. An oxide thickness of 10 nm is reached for 255 s process duration. We observe from Fig. 4 that the SiO<sub>2</sub> thickness increases

Fig. 4. Oxide thickness as a function of plateau time of 950 °C and 900 °C.

linearly with the process time for both oxidation temperatures. This agrees with thin  $SiO_2$  growth kinetics [22]. We also observe from this figure that for both temperatures the growth rates exhibit different slopes. The greatest is that of 950 °C. This is because the oxidation rate of 950 °C is higher than the one of 900 °C.

#### 3.2. NAOS growth

In this section, the objective is to grow a thin wet-chemical oxide of around 2 nm [15]. In our experiments, the SiO<sub>2</sub> layers were grown in HNO<sub>3</sub> solution using two-step oxidation method. The HNO<sub>3</sub> bath was temperature controlled and nitrogen-bubbled. Around 2 nm thick oxide was obtained for 80 min process duration.

#### 3.3. Silicon nitride film deposition

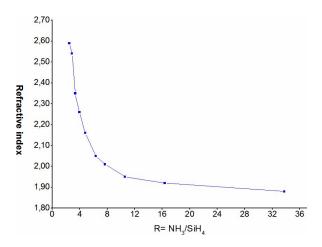

In order to vary the refractive index of the deposited layers, the ratio  $R = NH_3/SiH_4$  was varied in the range of 2.47 to 33.75, while keeping the total flow rate ( $NH_3 + SiH_4$ ) constant. All others parameters were kept constant. As the total gas flow rate is maintained constant, increasing of R means that the ammonia flow rate increases and silane flow rate decreases. This explains the decrease of the refractive index when the gas flow ratio increased as shown in Fig. 5. The silicon nitride film becomes less and less rich in silicon leading to N-rich films. As R varies from 2.47 to 6.31,

the refractive index decreases strongly in the range of 2.59 to 2.05 and then tends to saturate in the range of 7.68 to 33.75, corresponding to refractive index range of 2.01 to 1.88.

Fig. 5. Refractive index in a function of ammonia to silane flow rate ratio.

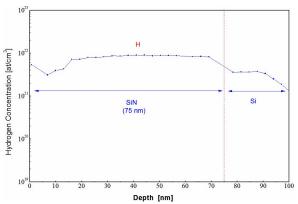

In order to avoid an additional silicon wafers load and unload steps which could cause handling damage of the very thin dielectric layers, the slow PECVD end-process phase (end of deposition step to wafers boat-out step) was used as an annealing step. During this phase the wafers were still under high temperature and at reduced pressure. Indeed, SIMS analysis of 75 nm thick SiN sample revealed that at the end of the deposition process, hydrogen atoms have moved to the silicon surface. This is illustrated in Fig. 6, where we observe that hydrogen atoms have diffused deep into the silicon substrate.

## 3.4. SiN/SiO<sub>2</sub> stack passivation

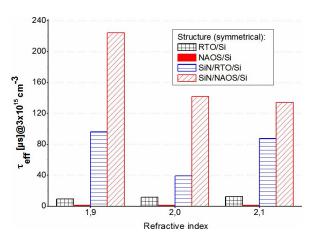

This section concerns silicon surface passivation by a double layer of SiN/SiO<sub>2</sub>. The RTO oxides were grown at 950 °C during 255 s as mentioned in section 3.1. The 2 nm NAOS oxides were grown by immersion of silicon wafers in the chemical bath of HNO<sub>3</sub>. Using both types of oxide and SiN films with three different refractive indices (1.9, 2.0 and 2.1), the SiN/SiO<sub>2</sub> stacks were fabricated. The SiN layers thicknesses were around 75 nm. Before processing, the effective minority carrier lifetimes in the wafers were between 10 μs

Fig. 6. SIMS depth profile of hydrogen in SiN/Si sample (refractive index of SiN: 2.0).

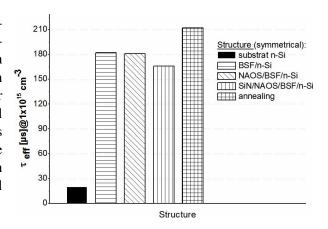

and 50  $\mu$ s. The  $\tau_{eff}$  values given in Fig. 7 present successive fabrication process steps for the three refractive indices. It is clear that both oxides with refractive index of 1.9 have the best passivation quality.

Fig. 7. Effective lifetime variation as a function of refractive index at successive steps of both structures fabrication. Injection level of  $3 \times 10^{15}$  cm<sup>-3</sup>.

It is known that the as-grown oxides give a very poor surface passivation. This is shown in Fig. 7, where we observe a significant degradation of  $\tau_{eff}$  for NAOS/Si. The quality of the passivation increased significantly after hydrogen-rich SiN deposition. We observe substantial increase of  $\tau_{eff}$  for the stacks capped with RTO oxides and very sharp rise in  $\tau_{eff}$  for the stacks capped with NAOS oxides. A value greater than 220  $\mu s$  was measured for

the stack with 1.9-SiN/NAOS/Si structure. Comparison of the passivation quality between both layers of oxides shows that the stack capped with NAOS oxide is much more efficient in passivation of silicon surface. The ratios of the minority carrier lifetimes are presented in Table 1. For the optimal refractive index (1.9), the NAOS method produces the passivation quality exceeding others by more than two times. Even if this method lasts more than three times longer, it represents the lowest thermal budget.

Table 1. Ratios of the minority carrier lifetimes and process duration.

| SiN<br>Refractive<br>index | τ <sub>eff</sub> ratio<br>(NAOS/RTO) | Process duration<br>ratio<br>(NAOS/RTO) |

|----------------------------|--------------------------------------|-----------------------------------------|

| 1.9                        | 2.3                                  | 2.75                                    |

| 2.0                        | 3.6                                  | 3.75                                    |

| 2.1                        | 1.5                                  |                                         |

The 2.0-SiN/NAOS stack was used to passivate 0.9  $\mu$ m depth a phosphorus back surface field (n-BSF). From Fig. 8 we observe that the deposition of n-BSF leads to an efficient passivation of the n-Si surface. The  $\tau_{eff}$  reached a value of 187  $\mu$ s. When capped with 2.0-SiN/NAOS stack and after annealing, the passivation effect of the BSF was improved. The  $\tau_{eff}$  increased to 212  $\mu$ s.

#### 4. Conclusions

In this paper, we investigated the SiN/SiO<sub>2</sub> stack surface passivation of n-type monocrystalline silicon surface. The passivation stacks were produced using both types of oxides (around 10 nm RTO growth and 2 nm NAOS growth) and SiN films with three refractive indices (1.9, 2.0 and 2.1). Concerning the last parameter, we found that stacks capped with 1.9-refractive index SiN films ensured the best passivation quality. We also found that stacks with NAOS oxides were the best passivation way to passivate n-type silicon surface. The minority carrier lifetime has more than doubled when a refractive index of 1.9 was used.

Fig. 8. Effective lifetime variation at an injection level of  $1 \times 10^{15}$  cm<sup>-3</sup> at successive steps of n-BSF passivation process.

Besides producing the most efficient passivation, NAOS technique has the lowest thermal budget. Based on these results, the SiN/SiO<sub>2</sub> stack using NAOS oxidation is the most advantageous way to passivate n-type silicon surface compared to thermal RTO method.

#### Acknowledgements

The authors gratefully acknowledge the financial support from the Directorate General for Scientific Research and Technological Development (Algerian Ministry of Higher Education and Scientific Research).

#### References

- [1] MAYET A.S., CANSIZOGLU H., GAO Y., GHANDI-PARSI S., KAYA A., BARTOLO-PEREZ C., ALHA-LAILI B., YAMADA T., PONIZOVSKAYA DEVINE E., ELREFAIE A. F., WANG S-Y., SAIF ISLAM M., JOSA B, 5 (2018), 1059.

- [2] EL AMRANI A., BEKHTARI A., EL KECHAI A., MENARI H., MAHIOU L., MAOUDJ M., SI-KADDOUR R., Superlattices Microstruct., 73 (2014), 224.

- [3] BALAJI N., LEE S., PARK C., RAJA J., NGUYEN H.T.T., CHATTERJEE NIKESH S.K., JEYAKUMAR R., JUNSIN Y., RSC Adv., 6 (2016), 70040.

- [4] GATZ S., PLAGWITZ H., ALTERMATT P.P., TERHEIDEN B., BRENDEL R., *Proc. 23rd EUPVSEC, Valencia, Spain*, 2008 (2008), 1033.

- [5] KAMINSKI P.M., ABBAS A., BASS K., CLAUDIO G., Energy Procedia, 10 (2011), 71.

- [6] LEBRETON F., Silicon surface passivation properties of aluminum oxide grown by atomic layer deposition for low temperature solar cells processes, Thesis, Université Paris-Saclay, 2017.

- [7] HAMEIRI Z., BOROJEVIC N., MAI L., NANDAKU-MAR N., KIM K., WINDERBAUM S., *IEEE J Photovolt.*, 7 (4) (2017), 996.

- [8] COTTER J. E., GUO J. H., COUSINS P. J., ABBOTT M. D., CHEN F. W., FISHER K. C., *IEEE T. Electron. Dev.*, 53 (8) (2006), 1893.

- [9] KIM K., DHUNGEL S. K., YOO J., JUNG S., MAN-GALARAJ D., YI J., J. Korean Phys. Soc., 51(5) (2007), 1659.

- [10] CUEVAS A., KERR M. J., SCHMIDT J., Proc. 3<sup>rd</sup> World Conf. Photovolt. Energy Convers., (2003), 913.

- [11] KERR M., CUEVAS A., Semicond. Sci. Technol., 17 (2) (2002), 166.

- [12] ZHAO J., Sol. Energ. Mater. Sol. C., 82 (53) (2004), 53.

- [13] RYU K., KIM S.-J., J. Korean Inst. Electr. Electron. Mater. Eng., 26 (1) (2013), 18.

- [14] KIM W.B., MATSUMOTO T., KOBAYASHI H., J. Appl. Phys., 105 (2009), 103709-1.

- [15] IMAMURA K., TAKAHASHI M. A., HIRAYAMA Y., IMAI S., KOBAYASHI H., J. Appl. Phys., 107 (2010), 054503.

- [16] HU Y.-C., CHIU M.-H., WANG L., TSAI J.-L., *Jpn. J. Appl. Phys.*, 49 (2) (2010), 022301-1.

- [17] LARIONOVA Y., HARDER N.-P., BRENDEL R., Proc. 25<sup>th</sup> EUPVSEC/5th World Conf. Photovolt. Energy Convers., Valencia, Spain, 2010 (2010), 1143.

- [18] LEGUIJT C., LÖLGEN P., EIKELBOOM J.A., WEEBER A.W., SCHUURMANS F.M., SINKE W.C., ALKEMADE P.F.A., SARRO P.M., MARÉE C.H.M., VERHOEF L.A., Sol. Energ. Mater. Sol. C., 40(4) (1995), 297.

- [19] CHEN Z., PANG S.K., YASUTAKE K., ROHATGI A., J. Appl. Phys., 74 (1993), 2856.

- [20] LIU C.P., CHANG M.W., CHUANG C.L., *Curr. Appl. Phys.*, 14 (2014), 653.

- [21] SCHMIDT J., KERR M., CUEVAS A., Semicond. Sci. Technol., 16 (2001), 164.

- [22] MASSOUD H.Z., PLUMMER J.D., IRENE E.A., J. Electrochem. Soc., 132 (11) (1985), 2693.

Received 2018-10-28 Accepted 2019-04-23