# ASSEMBLING A FORMULA FOR CURRENT TRANSFERRING BY USING A SUMMARY GRAPH AND TRANSFORMATION GRAPHS

# Bohumil Brtník<sup>\*</sup>

This paper deals with the symbolic solution of the switched current circuits. As is described, the full graph method of the solution can be used for finding relationships expressing current transfer, too. The summa MC-graph is constructed using two-graphs method in two-phase switching. By comparing the matrix form with results of the Mason's formula are derived relations for current transfers in all phases. There are discussed various options described transistor memory cells – with loss and lossless transistors and normal transistor current mirror. Evaluation of the graph is simplified if we consider the lossless transistors or if the  $y_{21}$ -parameter of one transistor is alpha multiple of second ones.

${\rm K~e~y~w~o~r~d~s:}~$  switched current, two phases, two-graph, Mason's formula, relations for current transfer, summary MC-graph

### **1 INTRODUCTION**

A switched-current (SI) system is defined as a system using analogue sampled-data circuits in which signals are represented by a current samples [1]. The basic building block of SI circuits is the current memory cell [2]. This can be described by the equation of time domain or by the z-transform of the operator z-domain. Current memory cell can be represented by graph, too.

Graph methods give results in a symbolic form [3, 4] which makes it can be used to finding general relations. One option is to find general relations for current transfer in switched current circuits in two-phase switching. General relations are used for the calculation method of matrix calculus of final solution. This method will be demonstrated in the example. The summa MC-graph is constructed using the transformation-graphs method [5], in two-phase switching, transformation-graphs method for switched capacitor circuits is described in [6] where the resulting relationship is in the shape of the matrix [7].

# 2 CALCULATION OF THE TRANSMISSIONS FROM THE SUMMARY GRAPH

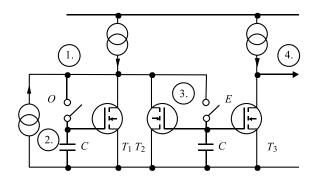

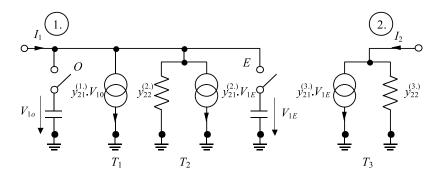

A circuit with a switched current has got for example the schematic wiring diagram shown in Fig. 1, eg [1,2]. This circuit consist of two capacitors C, and three field effect transistors  $T_1$ ,  $T_2$  and  $T_3$ , where  $T_1$  is lossless transistor. Phases of the switching are marked as odd and even, not 1 and 2, which could lead to confusion with the numbering of nodes and phases.

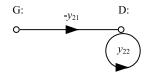

A solution of a circuit by the described method of a summary MC-graph [8] constructed on the transformation graphs [5] will be shown by solving a circuit with three field effect transistors and two capacitors, whose wiring diagram is shown in Fig. 1. The phases are marked as odd (O) and even (E) because numbered are the nodes. The field effect transistor is described by the equation  $I_D = y_{21}V_G + y_{22}V_D$ , this equation can be rewritten in the following form  $y_{22}V_D = -y_{21}V_G + I_D$ , if  $I_D = 0$  then  $y_{22}V_D = -y_{21}V_G$ . The graph representation of this equation [9] is in Fig. 2: The left side of the equation  $y_{22}V_{DS}$  represents the own loop of the node D with the transfer  $y_{22}$ , the right side branch going from the node G to the node D has the transition  $y_{21}$ . The lossless FET is described by the equation  $I_D = y_{21}V_G$ , it means in the graph representation will be one branch going from the node G to the node D with the transfer  $y_{21}$  only.

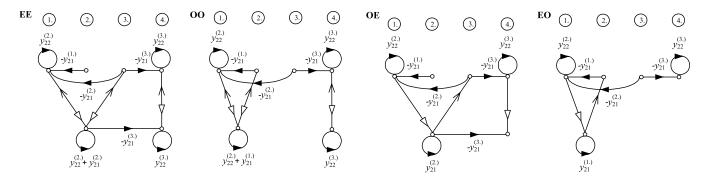

The circuit in Fig. 1 has four nodes, therefore the starting graph of the circuit in Fig. 3 has also four nodes. Full-graph solution is following:

Fig. 1. Schematic diagram of the SI circuit from the solution

Fig. 2. MC-graph of the equation  $y_{22}V_D = -y_{21}V_G$

Drain D of the transistor  $T_1$  is connected to the node 1, gate G to the node 2. Therefore, the transis-

<sup>\*</sup> Department of Electronics and Informatics, College of Polytechnics, Jihlava, CZ 586 01, brtnik@vspj.cz

Fig. 3. Transformation graphs for EE, OO, EO and OE phases

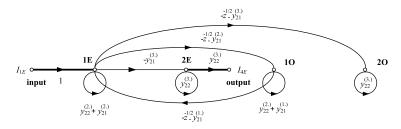

Fig. 4. The summary extended MC-graph

tor  $T_1$  is represented by the branch  $-y_{21}^{(1.)}$  from node 2 to node 1 and its inherent loop  $y_{22}^{(1.)}$  at the first node. Drain D of the transistor  $T_2$  is connected to the node 1, gate G to the node 3. Therefore, the transistor  $T_2$  is represented by the branch  $-y_{21}^{(2.)}$  from node 3 to node 1 and its inherent loop  $y_{22}^{(2.)}$  at the first node.

The branch between the nodes 3 and 1 with the transfer  $-y_{21}^{(2.)}$  is transformed to the inherent loop with the transfer  $y_{21}^{(2.)}$ , because in the relation  $a_I \tilde{y} a_V \alpha = y$  now  $\alpha = -1$ , as the branch of the original graph converts to the inherent loop in the resulting transformed graph. The inherent loop with the transfer  $y_{22}^{(1.)} + y_{22}^{(2.)}$  is transformed to the inherent loop, too. Because now  $\alpha = 1$ , the transfer is  $y_{22}^{(1.)} + y_{22}^{(2.)}$ , too. Therefore, the resulting transfer of its inherent loop is  $y_{22}^{(2.)} + y_{21}^{(2.)}$ .

The summary MC-graph is obtained from the partial transformed graphs from the Fig. 3 and is shown in Fig. 4.

First, the results of the transformed graphs for EE and OO phases are plotted as nodes with the inherent loops with transfers  $y_{22}^{(2.)} + y_{21}^{(2.)}$ ,  $y_{22}^{(3.)}$ ,  $y_{22}^{(2.)} + y_{21}^{(1.)}$  and  $y_{22}^{(3.)}$  and one branch with transfer  $-y_{21}^{(3.)}$ .

In the next step, the results of the transformed graph for the OE and EO phases multiplied by  $\pm z^{-\frac{1}{2}}$  are then drawn between these nodes as branches, *ie* the branch with the transfer  $z^{-\frac{1}{2}}(-y_{21}^{(3.)})$  between the nodes 1E and 2O, the branch with the transfer  $-z^{-\frac{1}{2}}y_{21}^{(2.)}$  between the nodes 1E and 1O, and the branch with the transfer  $-z^{-\frac{1}{2}}y_{21}^{(1.)}$  between the nodes 1O and 2E.

The current transfer  $\frac{I_{4E}}{I_{1E}}$  will now be obtained from an extended graph, *ie* a graph must be extended to two branches: the first branch from the input node IINP  $(I_{INP} = I_{1E})$  to the node 1E with transfer 1 and the second branch from the node 2E to the node  $I_{OUT}$   $(I_{4E} = I_{OUT})$ . The transfer is equal to the transmission of its own loop at the output node 2E, i.e.  $y_{22}^{(3.)}$  [6]. The summary MC-graph is now evaluated by means of the Mason's rule [3], the current transfer  $\frac{I_{4E}}{I_{1E}}$  is (1).

$$\frac{I_{OUT}}{I_{INP}} = \frac{I_{4E}}{I_{1E}} = \frac{\sum p_{(i)}\Delta_{(i)}}{V - \sum S^{(K)}V^{(K)}} = 1 \\

1 \left(-y_{21}^{(3.)}\right) y_{22}^{(3.)} \left(y_{22}^{(2.)} + y_{21}^{(1.)}\right) y_{22}^{(3.)} \times 1 \\

1 \left/ \left( \left(y_{22}^{(2.)} + y_{21}^{(2.)}\right) y_{22}^{(3.)} \left(y_{22}^{(2.)} + y_{21}^{(1.)}\right) y_{22}^{(3.)} - z^{-\frac{1}{2}} y_{21}^{(2.)} z^{-\frac{1}{2}} y_{21}^{(1.)} y_{22}^{(3.)} y_{22}^{(3.)} \right) \\

= \frac{-y_{21}^{(3.)} \left(y_{22}^{(2.)} + y_{21}^{(1.)}\right)}{\left(y_{22}^{(2.)} + y_{21}^{(1.)}\right) \left(y_{22}^{(2.)} + y_{21}^{(1.)}\right) - z^{-1} y_{21}^{(2.)} y_{21}^{(1.)}} \quad (1)$$

## **3 MATRIX DESCRIPTION**

The linearized diagram of the circuit from the Fig. 1. is drawn in Fig. 5 and can be described by nodal admittance formulation by matrix (2).

$$V_{1E}: V_{2E}: V_{1O}: V_{2O}:$$

$$I_{1E}: \begin{bmatrix} y_{22}^{(2.)} + y_{21}^{(2.)} & 0 & z^{-\frac{1}{2}} y_{21}^{(1.)} & 0 \\ y_{21}^{(3.)} & y_{22}^{(3.)} & 0 & 0 \\ \hline z_{1O}: \begin{bmatrix} z^{-\frac{1}{2}} y_{21}^{(2.)} & 0 & y_{22}^{(2.)} + y_{21}^{(1.)} & 0 \\ z^{-\frac{1}{2}} y_{21}^{(3.)} & 0 & 0 & y_{22}^{(3.)} \end{bmatrix}$$

$$(2)$$

$$(2)$$

Fig. 5. Linearized diagram of the circuit from the Fig. 1

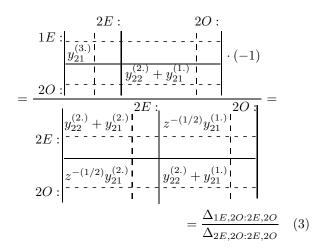

In the next step, the elements occurring in the numerator and denominator of the relation (1) are written into the corresponding positions in which they are in the matrix (2). Because the nodes of Fig. 1 are renumbered in Fig. 5, when  $4 \rightarrow 2$ , transfers of the currents after renumbered are following:  $\frac{I_{4E}}{I_{1E}} \rightarrow \frac{I_{2E}}{I_{1E}}$ ,  $\frac{I_{4O}}{I_{1E}} \rightarrow \frac{I_{2O}}{I_{1O}}$ ,  $\frac{I_{4E}}{I_{1O}} \rightarrow \frac{I_{2O}}{I_{1O}}$ . So will for transfer  $\frac{I_{2E}}{I_{1E}} = \frac{-y_{21}^{(3.)}(y_{22}^{(2.)} + y_{21}^{(1.)})}{(y_{22}^{(2.)} + y_{21}^{(1.)}) - z^{-1}y_{21}^{(2.)}y_{21}^{(1.)}} =$

336

By comparing with the matrix (2) it is now apparent that in the numerator there is an algebraic complement of this matrix (2) created out of this matrix by leaving out the rows 1*E* and 2*O* and the columns 2*E* and 2*O*, symbolically written  $\Delta_{1E,2O:2E,2O}$ . In the denominator, there is then the algebraic complement of the matrix (2) created out of this matrix by leaving out the rows 2*E* and 2*O* and the columns 2*E* and 2*O*, symbolically written  $\Delta_{2E,2O:2E,2O}$ .

According to the theory of multiple algebraic complements [3], the sign (-1) in the numerator gives the number of omitted odd indices, in the numerator the row 1Eis omitted, which is the first (odd index) row in the matrix, while the remaining row 2O is even in the row as well as the omitted column 2E, which is the second column in the matrix, and the column 2O, which is the fourth column in the matrix. In the denominator the omitted rows 2E and 2O and columns 2E and 2O are the second and fourth rows and columns in the matrix, *ie* they always have even indices, which then corresponds to a positive sign.

#### 6 CONCLUSIONS

A unified method in analyzing switched current circuits is presented. As can be seen, the description of different types of memory cells can be used for the assembling of the general relations. The advantages of this approach are in its uniformity in deriving results from graph. By comparing the results from the matrix and results obtained from the Mason's formula are derived general relations for current transfers. The described method can be used for solving and understanding of simple circuits.

#### References

- SHAAH, P.—TOUMAZOU, C.: Analysis and Design of Speed and Dynamic Range in Switched Current Cells, Circuits and Systems Tutorials, IEEE Press, New York, 1996, pp. 487–513.

- [2] MARTINEK, P.—BOREŠ, P.—HOSPODKA, J.: The Electric Filters, CTU Publisher, Prague, 2003.

- [3] ČAJKA, J.: The Circuits Theory. Linear Circuits, SNTL/ALFA, Prague, 1979.

- [4] GRIMBLEBY, J., B.: Symbolic Analysis of Circuits Containing Active Elements, Electronics Letters 17 No. 20 (1981), 754–756.

- [5] BIOLEK, D.—BIOLKOVA, V.: Analysis of Circuits Containing Active Elements by using Modified T-graphs, In N. E. Mastorakis and L. A. Pecorelli-Peres, Advances in Systems Science: Measurement, Circuits and Control, WSEAS Press, Electrical and Computer Engineering Series, 2001, pp. 279–283.

- [6] DOSTÁL, T.: The Analysis of the Active Components Containing Switched Capacitors by Nodal Voltage Method, Electronics Horizont 45 No. 1 (1984), 21–26.

- [7] VLACH, J.—SINGHAL, K.: Computer Methods for Circuit Analysis and Design, 2<sup>nd</sup> ed., Van Nostrand Reynhold, New York, 2003.

- [8] BRTNÍK, B.: Full-Graph Solution of Switched Circuits, Lambert Academic Publishing GmBH, Saarbrucken, 2011.

- [9] BIOLEK, D.: Solving Eelectronics Circuits, BEN Publisher, Prague, 2004.

Received 25 June 2012

Bohumil Brtník, biography not supplied.