# Design of AC-DC Grid Connected Converter using Multi-Objective Optimization

Szymon Piasecki (*PhD Student, Warsaw University of Technology*), Robert Szmurlo (*Assistant Professor, Warsaw University of Technology*), Marek Jasinski (*Assistant Professor, Warsaw University of Technology*)

Abstract - Power electronic circuits, in particular AC-DC converters are complex systems, many different parameters and objectives have to be taken into account during the design process. Implementation of Multi-Objective Optimization (MOO) seems to be attractive idea, which used as designer supporting tool gives possibility for better analysis of the designed system. This paper presents a short introduction to the MOO applied in the field of power electronics. Short introduction to the subject is given in section I. Then, optimization process and its elements are briefly described in section II. Design procedure with proposed optimization parameters and performance indices for AC-DC Grid Connected Converter (GCC) interfacing distributed systems is introduced in section III. Some preliminary optimization results, achieved on the basis of analytical and simulation study, are shown at each stage of designing process. Described optimization parameters and performance indices are part of developed global optimization method dedicated for AC-DC GCC introduced in section IV. Described optimization method is under development and only short introduction and basic assumptions are presented. In section V laboratory prototype of high efficient and compact 14 kVA AC-DC converter is introduced. The converter is elaborated based on performed designing and optimization procedure with the use of silicon carbide (SiC) power semiconductors. Finally, the paper is summarized and concluded in section VI. In presented work theoretical research are conducted in parallel with laboratory prototyping e.g. all theoretical ideas are verified in laboratory using modern DSP microcontrollers and prototypes of the AC-DC GCC.

*Keywords* – AC-DC power converters; Silicon carbide; Design optimization; Pareto optimization.

#### I. INTRODUCTION

Increasing number of Renewable Energy Sources (RESs) and distributed Active Loads (ALs) called Distributed Systems (DSs) connected to the electrical grid causes common use of power electronic AC-DC converters. Voltage Source Converter (VSC) is nowadays one of the most popular solutions used to connect distributed systems to the electrical grid. VSC which operates as a grid interface is called Grid Connected Converter (GCC) [1]. For proper and efficient operation of the connection between the grid and DS parameters of the converter need to be specified and designed precisely according to operation conditions and desired properties of the interface [2]. Moreover problems related to power quality and grid stability needs to be taken into account during the design process [1], [3] as well as possibilities given by new materials and technologies [4], [5] and [6]. Making a conclusion - design of the GCC is complex and difficult task, demanding consideration of many system variables

(parameters) to achieve desired system properties. To obtain system parameters satisfying all design objectives on desired level additional tools are employed into design process. As the most convenient mathematical tool, which can support the designer in the process of decision making and analysis of all possible choices, Multi-Objective Optimization can be used [6], [7] and [8].

#### II. ELEMENTS OF THE OPTIMIZATION PROCESS

The MOO is a mathematical tool known from economics, which gives possibility to find family of solutions fulfilling the established requirements (objectives) in the best way. The MOO methods being very fast growing and developing areas of science, recently have been implemented in many engineering fields, where for solving complicated design problems with contrary design objectives are used. An area where MOO can be successfully implemented is power electronics [6]. In case of the GCC design as a result of optimization process set of converter parameters is expected. Optimization objectives are the requirements and functionalities requested from the GCC interface.

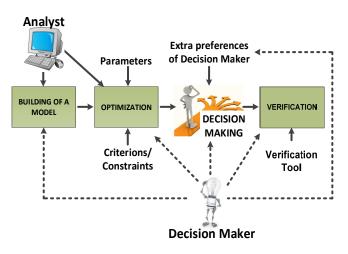

The optimization process involves: model of considered system and its parameters, objectives and constraints, decision maker and analyst. Elements of the MOO are described below [6], [7].

## A. Model of a Considered System

Proper and accurate model of considered problem is the most important part of the optimization process. To build accurate model of the system composed from many variables and parameters is a challenging task, and very often to realize the optimization itself is more important and difficult. As a matter of fact, increasing computational speed of modern computers and also very dynamically growing market of modeling/optimization software gives into designer's hands tools allowing quick creation of various variants of models for the analyzed system. In the field of power electronics many software packages are available: Matlab with Simulink and PLECS libraries, Synopsys Saber, PSIM, Gecko Circuits, Maple, OPES, and others. Almost each of them has some built-in optimization libraries, moreover some additional software dedicated only for optimization can be also used [9]-[15]. Very often integration of two or more simulation environments is necessary to model all system phenomena (like thermal behaviour, electrical behaviour, geometrical placement of elements, etc.) [16], [17].

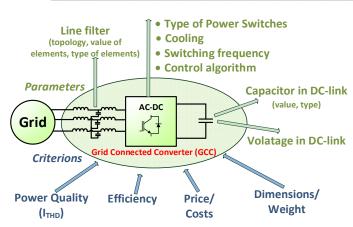

Fig. 1. Selected optimization parameters (variables) and objectives (criterions) for grid connected AC-DC converter (GCC).

## B. Parameters (Variables)

Another important part of the optimization process is the system parameters. As an optimization parameter each system variable which is taken into consideration by optimization algorithm is understood. In the case of described GCC the considered optimization parameters are marked in Fig. 1. By the optimization procedure type of used power semiconductors or DC-link capacitors (converter elements) as well as DC-link voltage level or switching frequency (converter variables) are treated as optimization parameters having influence on the properties of the designed system.

### C. Objectives and Constraints

Optimization objectives are properties and functionalities of the system which designer wants to achieve. In the case of considered GCC main goals of the design process are: to increase power quality and overall efficiency of the converter as well as to minimize volume and price of the system (Fig. 1). Mathematical representation of an objective is the performance index (or cost index). Performance indices define performance space of the designed system, which for power electronics converters design are [6]:

- 1. Efficiency of the system, expressed by:

- a. Overall efficiency:

$$\eta = \frac{P_o}{P_I} [p.u.], \qquad (1)$$

where  $P_O$  – output power,  $P_I$  – input power.

b. Relative losses:

$$\frac{P_L}{P_O} = \frac{1-\eta}{\eta} [p.u.], \qquad (2)$$

where  $P_L$  – system losses,  $P_O$  – output power,  $\eta$  – efficiency.

**2.** Power quality of the processed energy, expressed by output current / voltage THD factors  $(I_{THD} / U_{THD})$ ;

- 3. Volume / Weight of the system, expressed by:

- c. Power Density Factor ( $\rho$ ):

$$\rho = \frac{P_{O,N}}{V_G} \left[ \frac{kW}{dm^3}, \frac{kVA}{dm^3} \right], \tag{3}$$

where  $P_{O,N}$  – rated output power,  $V_G$  – overall volume of the system.

d. Output Power per Unit Weight ( $\gamma$ ):

$$\gamma = \frac{P_o}{W_G} \left[ \frac{kW}{kg}, \frac{kVA}{kg} \right],\tag{4}$$

where  $P_O$  – output power,  $W_G$  – overall weight of the system.

- 4. Price of the system, expressed by:

- e. Relative Costs ( $\sigma$ ):

$$\sigma = \frac{P_o}{C_G} \left[ \frac{kW}{\$}, \frac{kW}{€} \right], \tag{5}$$

where  $P_O$  is an output power,  $C_G$  – given cost.

In some designing approaches performance index can be expressed in the form of constraint. Constraint is a limit maximal or minimal value specified by the designer for selected objective [16].

For the most popular optimization approaches system objectives, expressed by performance indices are joined into a cost function [6]-[8]. In this approach all considered objectives are components of single, global cost function which has to be minimized (or maximized) by the optimization procedure. Significance of each objective is adjusted by the weighting coefficients and the cost function can be expressed as follows:

$$\min(\alpha_1 \cdot f_1 + \alpha_2 \cdot f_2 + \dots + \alpha_n \cdot f_n), \qquad (6)$$

where  $\alpha_1, \alpha_2, ..., \alpha_n$  are weighting coefficients,  $f_1, f_2, f_n$  are performance indices.

Adjustment of weighting coefficients is specified according to designer preferences as a part of optimization process.

#### D. Decision Maker

Decision Maker (DM) is another part of the process. It is a person with expert knowledge from the field of optimized problem. Based on his knowledge and experience the DM is able to analyze non-dominated results obtained by the optimization procedure (Fig. 3) and select the best ones according to his preferences. He can also restrict design objectives by proper adjustment of weighting coefficients in cost function and setting selected performance indices on desired level (constraints). The DM is also responsible for verification of the results obtained by the optimization. He has to validate that parameters calculated by the mathematical procedure are reachable for real elements/system. The verification is very important part of the optimization process.

2014/5

Fig. 2. Basic elements and steps of the optimization process.

It gives a feedback that obtained by mathematical calculations results can be used in practice. For more complex optimization problems with many parameters and objectives advanced verification tools have to be used. In case of the GCC it can be a simulation model of considered system/device and/or a laboratory prototype.

#### E. Analyst

The analyst is a person or a computer program responsible for mathematical modelling of the considered problem. Analyst should be able to present and illustrate the developed model and steps of optimization algorithm in a way easy to understand and interpret for the DM.

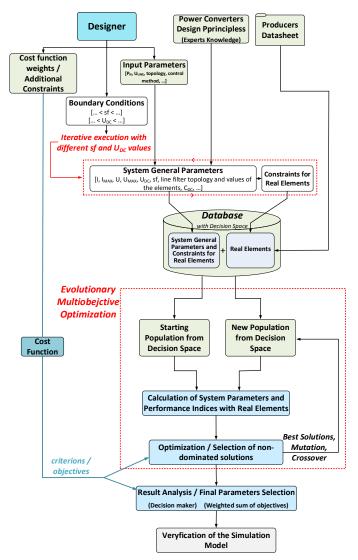

Basic elements and steps of the optimization process are presented in Fig. 2.

# F. Results

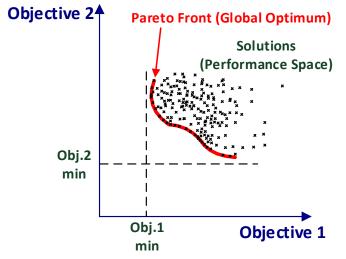

There are many methods for solving multi-dimensional problems, thanks to increasing computation speed and advancement of programming tools it is an area of very fast growing new computational methods and algorithms [7], [18] and [19]. For optimized system there is no single, optimal solution, but a set of different solutions, different trade-offs.

Fig. 3. Results of discrete optimization - Pareto Front (Global Optimum).

The objective of applied optimization methodology is to find such results (in this case a set of GCC's parameters) for which an improvement of any objective makes others worse, for selected criterions giving Global Optimum, called also Pareto Front [6] and [7], marked in Fig. 3.

## III. DESIGN OF 3-PHASE GRID CONNECTED AC-DC CONVERTER

In this section design procedure for the GCC is proposed. Design technique and provided equations are dedicated for two-level AC-DC VSC. For each described and analyzed component of the converter performance indices are proposed. Indices are used to validate analyzed element and select design parameters (results) the best fulfilling designer requirements. Presented design methodology is a part of procedure for global AC-DC GCC parameters calculation and optimization [19]. Concept of developed procedure is presented in the next section. The procedure is elaborated to be executed iteratively by the optimization algorithm with different values of two main designing parameters – converter's DC-link voltage level ( $U_{DC}$ ) and switching frequency ( $f_{SW}$ ). With variations of these parameters in specified range the GCC parameters are obtained in the following steps:

#### A. Input Parameters

For the procedure initial parameters specified by the designer are used:

- RMS value of the grid voltage (U<sub>GRID</sub>) and grid angular frequency (ω<sub>0</sub>) – for designed system respectively;

- nominal power (P<sub>N</sub>) value of nominal power for considered system, expressed in Watts, based on this value and grid voltage RMS current under nominal load (I<sub>RMS</sub>) is calculated;

- boundary conditions specified by the designer range for changes of DC-link voltage level (U<sub>DC</sub>) and switching frequency (f<sub>SW</sub>);

- design objectives preferences of the designer related to applied in the optimization procedure performance indices.

Preferences are expressed by weighting coefficients for design objectives implemented in the cost function.

## B. Line Filter

## Design Methodology

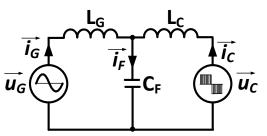

First step of the designing procedure is calculation of the line filter parameters according to given  $U_{DC}$  and  $f_{SW}$ . As a line filter LCL topology is used. Single-phase equivalent circuit of the VSC with the LCL filter is presented in Fig. 4. The transfer function of the filter is given in [20].

Fig. 4. Single-phase equivalent circuit of the VSC with LCL filter.

2014/5

The filter parameters calculations are based on [20] and [21]. Input parameters specified according to design objectives are: maximum ripple current on converter side inductor (*RippC*), maximum ripple current on the grid side inductor (*RippG*) and maximum reactive power absorbed by the filter ( $Q_F$ ). The filter parameters are calculated in the following steps:

**1.** Converter side inductance (*L<sub>C</sub>*) calculation according to *RippC*:

$$L_{C} = \frac{U_{DC}}{6 \cdot RippC \cdot \sqrt{2} \cdot I_{RMS} \cdot f_{SW}},$$

(7)

where  $U_{DC}$  is DC-link voltage level, RippC – specified ripple current,  $I_{RMS}$  – nominal current of the GCC and  $f_{SW}$  – switching frequency.

**2.** Filter capacitance  $(C_F)$  calculation:

$$C_F = \frac{Q_F \cdot P_N}{3 \cdot \omega_0 \cdot U_{GRID}^2},\tag{8}$$

where  $Q_F$  is specified maximum value of reactive power consumed by the filter,  $P_N$  – nominal power of the designed system.

**3.** Grid side inductance  $(L_G)$  calculation with use of equation given in [20] according to specified ripple current on the grid side inductor (RippG):

$$L_{G} = \left| \frac{1 - RippG}{RippG \cdot \left[ 1 - \left( L_{C} \cdot C_{F} \cdot \left[ 2 \cdot \pi \cdot f_{SW} \right]^{2} \right) \right]} \right| \cdot L_{C} .$$

(9)

## Performance Index

For evaluation of the designed line filter the following performance indices are used:

1.  $V_{LCL}$  – index related to the volume of filter components, estimated on the basis of peak energy with scaling factors described in [22]. For analyzed LCL filter is expressed as follows:

$$V_{LCL} = \frac{1}{2} \cdot SF_C \cdot C_F \cdot U_{GRID}^2 + \frac{1}{2} \cdot SF_L \cdot (L_C + L_G) \cdot I_{G_-MAX}^2,$$

(10)

where  $SF_C$  and  $SF_L$  are scaling factors for capacitors and inductors respectively,  $I_{G\_MAX}$  is maximal  $L_C$  current according to ripple current RippC, expressed as:

$$I_{G_{-MAX}} = I_{RMS} + (RippC \cdot I_{RMS}).$$

(11)

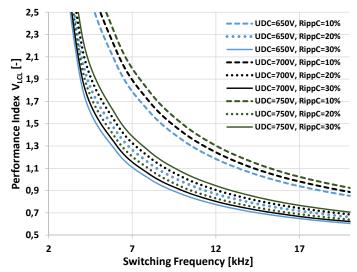

Variations of  $V_{LCL}$  local performance index for different values of switching frequency ( $f_{SW}$ ), DC-link voltage ( $U_{DC}$ ) and ripple current in percent (RippC) for the 14 kVA converter design are presented in Fig. 5. Scaling factors are related with selected material and component technology and for analyzed case are equal to 1.11 m<sup>3</sup>/kJ for inductors and 0.54 m<sup>3</sup>/kJ for capacitors [22].

Fig. 5. Variations of  $V_{LCL}$  performance index for different switching frequencies with changes of  $U_{DC}$  and *RippC* parameters. Analysis performed for 14 kVA converter design.

2.  $P_{LCL}$  – index related to the losses in the line filter. For the LCL filter the main source of losses are inductors, while losses in the capacitors are relatively small and they are omitted. Losses of the inductors are obtained according to (12):

$$P_{LCL} = P_{core} + P_{wind} , \qquad (12)$$

where  $P_{core}$  are the losses in the magnetic core and  $P_{wind}$  are losses in the windings.

Dominating are the core losses, which are estimated with the use of Steinmetz formula [23] as follows:

$$P_{core} = k \cdot f_{SW}^m \cdot B_{ac}^n, \qquad (13)$$

where  $B_{ac}$  is the peak AC flux density with switching frequency  $f_{SW}$ , and k, m, n are Steinmetz Equation (SE) parameters. SE parameters related to the materials are obtained on the basis of datasheets. Peak AC flux density  $B_{ac}$  is calculated as follows [24]:

$$B_{ac} = I_{Lm} \frac{\mu_{rC} \cdot \mu_0 \cdot L}{V_{core}}, \qquad (14)$$

where  $I_{Lm}$  - current through magnetizing inductance,  $\mu_{rC}$  - relative core permeability,  $\mu_0$  - permeability of vacuum,  $V_{core}$  - core volume.

It should be noted that eq. (14) gives high accurate results only for sine and symmetrical triangular waveforms [25] and this performance index will be evaluated during development of the optimization procedure.

# C. DC-link Capacitor

## Design Methodology

In the next step of the designing procedure DC-link capacitor of the converter is calculated. The purpose of the DC-link capacitor is to stabilize the voltage in DC circuit by delivery high currents especially during transients. In the paper considered nominal voltage is from 560 up to 900 V DC. The capacitor in DC-link application should have

sufficiently long life time, usually not shorter than 20 khours (c. 3 years) the best longer than 100 khours (c. 12 years). The operation of the capacitors in DC-link is usually with high temperature due to proximity of power semiconductor switches. Therefore, a designer should take the following issues into consideration: 1) capacitance and voltage level; 2) the switching frequency range of power electronics devices; 3) ripple current value; 4) ambient temperature and cooling type (e.g. natural convection, forced cooling or cold plate); 5) resistances and inductances needs; 6) mechanical reliability; 7) shape, volume and connections type; 8) relative costs; 9) casing etc. [26]-[30]. In proposed design methodology value of the capacitance  $C_{DC}$  is obtained with use of equation (15) given in [31]. Input parameter for the calculations specified according to design objectives is  $RippU_{DC}$ , which determines desired ripples of DC-link voltage

$$C_{DC} = P_N \cdot \frac{\sqrt{2} + \frac{3 \cdot U_{GRID}}{U_{DC}}}{6 \cdot Ripp U_{DC} \cdot U_{DC} \cdot f_{SW} \cdot U_{GRID}}.$$

(15)

## Performance Index

For evaluation and selection of the DC-link capacitor type the following performance indices are used:

V<sub>C\_DC</sub> – index related to the volume of DC-link capacitors based on peak energy with scaling factor related to the type of the material and technology (SF<sub>DC</sub>):

$$V_{C_{DC}} = \frac{1}{2} \cdot SF_{DC} \cdot C_{DC} \cdot U_{DC}^2.$$

(16)

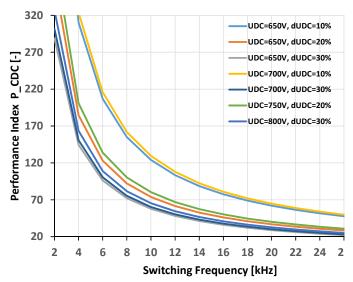

**2.**  $P_{C_{DC}}$  - index related to the losses of DC-link capacitor, Fig. 6. Assuming that the core temperature is equal to case temperature (for simplicity) capacitor power loss can be expressed as follows:

$$P_{C_{DC}} = I_{Ripp\_RMS}^2 \cdot ESR_{C_{DC}}, \qquad (17)$$

where  $I_{Ripp\_RMS}$  is capacitor ripple current,  $ESR_{C\_DC}$  is

Fig. 6. Variations of  $P_{CDC}$  performance index for different switching frequencies with changes of  $U_{DC}$  and  $RippU_{DC}$  parameters. Analysis performed for 14 kVA converter.

Equivalent Series Resistance of the capacitor described in producers datasheet or expressed as follows:

$$ESR_{C_{DC}} = \frac{\tan \delta}{2 \cdot \pi \cdot f_{SW} \cdot C_{DC}},$$

(18)

where  $\tan \delta$  – dissipation factor,  $f_{SW}$  - switching frequency,  $C_{DC}$  – DC-link capacitance.

3.  $L_E$  – capacitors life time (or Life Expectancy) index which can be derived from [26] as:

$$L_E = L_N \cdot \left(\frac{V_N}{V}\right)^8,\tag{19}$$

where:  $L_E$  - Life Expectancy at operating voltage V,  $L_N$  - life expectancy at nominal voltage  $V_{N_1}$ ,  $V_N$  - nominal voltage, V - operating voltage.

Another parameter which describes capacitor properties is Equivalent Series inductance (ESL) given in producers datasheet. This parameter should be as small as possible because stray inductance on the current path from the DC-link to the DC capacitor banks and to the power semiconductors should be as short as possible especially for higher switching frequency like in case of applied SiC devices. High stray inductance can limit the switching frequency and cause unstable operation (oscillations, resonances etc.) which, in turn increases temperature and reduces time between failures.

In modern power electronic converter two main types of the capacitors are used: electrolytic capacitors and film capacitors. Because of higher life time factor film capacitors are nowadays most often used. Selected properties of film and electrolytic capacitors are collected in Tab. I. In case of power electronics application the most frequently used in film capacitors dielectric is Polypropylene (PP) because assures lowest ESR, hence lowest heat increase  $\Delta T$ . Moreover, in the case of failure gives an open circuit. Its reliability is high. In PP there is no piezoelectric effect and polarity is not important. There is also possibility to use less costly Polyethylene Terephthalate (PET). However PET material has dissipation factor  $tan\delta$  about ten or more times higher than PP material while the cost of PP is about 15% higher than PET. In case of Polyethylene Sulfite (PPS) or Polyethylene Naphthalate (PEN) the cost seems to be not acceptable in classical applications (c. 7 and 3 times more expensive).

FILM AND ELECTROLYTIC CAPACITOR MAIN PROPERTIES [26], [29] [30] Electrolytic Parameter Film Capacitor Capacitor <500V <2200V DC Voltage <190khours <50khours<sup>A</sup> Life time ESR or dissipation factor Lower Higher (typically c.20 times) tan δ Ripple current I<sub>Rip\_RMS</sub><sup>B</sup> Higher Lower (c. 2 times or more) Capacitance Lower Higher Lower (c. 4 to 10 times) Energy density (J/cm3) Higher ESL Lower Higher Price Higher Lower

TABLE I

Film and Electrol vtic Capacitor Main Properties [26] [29] [30]

Legend: A - with high capacitance C derating; B - natural convection cooling

#### 2014/5

## D. Semiconductors

## <u>Design Methodology</u>

The next step of the designing procedure is the selection of power switches of the converter. Selection of the semiconductors is complex task related with many correlated variables. The most important factors which have influence on the semiconductors selection are:

- desired converter properties expressed by performance indices described in section II: power density factor, volume/weight factor, efficiency and power quality factor;

- **2.** price of the element and related to it expected price of the whole designed converter;

- **3.** availability of the selected element on the market, continuity of supply by the producers;

- **4.** additional requirements, like EMI compatibility standards or noise reduction and related with them forced operation conditions of the converter in example switching frequency range or DC-link voltage level.

On the market a designer has a wide choice of power semiconductors, with different properties and prices. Moreover new technologies are introduced like SiC or GaN transistors which seems to be very promising alternative to silicon structures [5], [6]. To be up to date with all possible choices and solutions continuous observation of the market has to be done. Thus, the idea of a database where the available for the designer elements and their properties are stored could be very convenient [19]. Concept of the database implemented in the optimization procedure is introduced in section IV.

## Performance Index

For evaluation and selection of available power semiconductors losses of the switching device should be calculated. This factor gives information about size of a needed heat sink, expected efficiency and volume of the converter. In the proposed design methodology the following index is used:

$P_{SEM}$  - index related to the losses in semiconductor.  $P_{SEM}$  losses are composed by switching losses ( $P_{SW}$ ) and conducting losses ( $P_{CON}$ ) and summarized as follows:

$$P_{SEM} = P_{SW} + P_{CON} \,. \tag{20}$$

Switching losses estimation is based on the parameters obtained from datasheets provided by the producers and equations describing the power losses of three-phase VSC [32]. The switching power loss of the converter operating with standard Space Vector PWM may be described as:

$$P_{SW} = \frac{6}{\Pi} \cdot f_{SW} \cdot (E_{ON} + E_{OFF} + E_{REC}) \cdot \frac{I_M}{I_{RMS}} \cdot \frac{U_{DC}}{U_N}, \qquad (21)$$

where:  $E_{ON}$ ,  $E_{OFF}$  and  $E_{REC}$  are switching energies of the transistor and diode, tested at nominal voltage  $U_N$  and nominal current  $I_{RMS}$ . The AC-DC converter operates at DC voltage  $U_{DC}$ , peak phase current  $I_M$  and switching frequency  $f_{SW}$ .

The conduction power losses are obtained with the use of simplified equation for conduction power loss expressed as:

$$P_{CON} = 3 \cdot I_{RMS}^2 \cdot r_{ON} , \qquad (22)$$

where on-state resistance  $r_{ON}$  parameter is obtained from the datasheet.

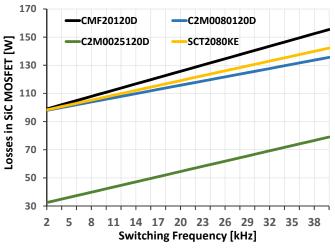

For a design of 14 kVA high efficient and compact AC-DC GCC silicon carbide power MOSFETs have been analyzed according to the described methodology. For selected power range CMF2012D and C2M0080120D MOSFETs from Cree [33] and SCT2080KE MOSFET from Rohm [34] have been analyzed. The obtained results for  $I_{RMS}$ =20A,  $U_{DC}$ =800V in frequency range 2-40 kHz are presented in Fig. 7. According to the lowest overall losses C2M0080120D power semiconductor has been selected for laboratory investigation. During development of a prototype converter and after selection of the switching device new MOSFET with  $r_{on}$ =25mOhm – C2M0025120D – has been provided by Cree. Its properties have been also included in Fig. 7 for comparison.

Fig. 7.  $P_{\text{SEM}}$  performance index for analyzed SiC power MOSFETs in switching frequency range 2-40 kHz.

#### E. Control Method

From the point of view of converters hardware design selection of the applied control method is not a key task, but has some influene on the designed system. Advanced control strategies give additional functionalities to the designed system. In the case of the GCC which suplies distributed system no negative impact to the electrical grid, high efficiency and robustness for grid voltage disturbances like dips and high order harmonics are expected. To achieve this functionalities modular vector control should be implemented with additional modules in the main control scheme like harmonics compensation module, voltage dips compensation module and reactive power compensation module [1]. From the converter hardawre design additional functionalities may require sufficient DC-link voltage level (eg. 700V instead of 650V), higher switching frequencies (for harmonics compensation) or additional current/voltage sensors. Moreover DSP controller should provide sufficient calculation capacity and memory, thus DSP procesors like TI TMS Delfino family can be used.

## IV. OPTIMIZATION OF AC-DC GRID CONNECTED CONVERTER

In this section a concept of the MOO procedure dedicated for design of three-phase AC-DC GCC is introduced. Brief view of optimization methods and approaches applied in the field of power electronics is given by the authors in [19]. According to the analyzed optimization approaches objectives for the developed procedure are as follows:

- the procedure should take into account only real, available on the market elements. Thus, a database with elements properties and parameters should be created and integrated with the optimization tool. Parameters of elements described on basis of datasheets provided by the producers. Possibility of easy adding new elements and materials to the developed database should be assured;

- optimization process should take relatively short time. Thus, discrete optimization with evolutionary algorithms should be used for main optimization calculations;

- procedure should operate as a web application, without additional optimization software;

- no necessity of laboratory measurement for extracting selected materials and elements parameters;

- low complexity of the developed mathematical models (saving computation effort and time).

The objective of presented work is to create an optimization algorithm, which can be used as a supporting tool in the case of the GCC design. The developed tool should give to the engineer a general view of the designed system and ability to observe how changes of one or more parameters will effect on the system properties. To avoid phase of feasibility study and to be as close as possible to the industrial solutions the parameters should represent real, available on the market components. The set of solutions is focused only on the standardized products available on the market (cores, wires diameters, semiconductors types, heat-sinks shapes, capacitors etc.). Another assumption is that optimization calculations should take relatively short time. Obtained system parameters calculated as presented in sections II and III are inputs for developed procedure of global parameters optimization for the GCC. Concept of proposed optimization method is presented in Fig. 8. Calculated system parameters create an input vector for the optimization procedure marked in Fig. 8 as "System General Parameters". For calculated general parameters constraints for possible to use real elements are obtained. Based on manufacturers datasheets of selected elements (semiconductors, capacitors, magnetic materials, etc.) database with parameters of real elements is created. Thanks to implementation of evolutionary algorithms [35] several scenarios for designed system with different parameter sets can be obtained. For each set of parameters the performance indices and global cost function value are calculated. To join different performance indices in one global cost function weighted coefficients are employed. The procedure requires further investigations and research with regard to selection of the most appropriate evolutionary algorithm and adjustment of weighting coefficients for the cost function. The authors assume that a designer of industrial device is interested in the

elements available on the market only and even only in the selected part (standardized) of them. In this case the elements under consideration of the designer only will be selected to the database. By management of the elements stored in database the designer can have continuous insight and control on the elements analyzed by the procedure. The database can be continuously updated and new materials available on the market can be added.

The generated system parameters should be verified on simulation model (like Matlab-Simulink, Plecs or Synopsys Saber simulation environments). To evaluate operation of the optimization procedure prototype of the "optimized" device can be constructed and verified with a series of laboratory tests. The obtained results allow to verify proper operation of the developed MOO procedure and adjust weighting coefficients of the evolutionary algorithm and cost function.

Fig. 8. Proposed Multi-Objective Optimization (MOO) procedure for Grid Connected Converter (GCC).

2014/5

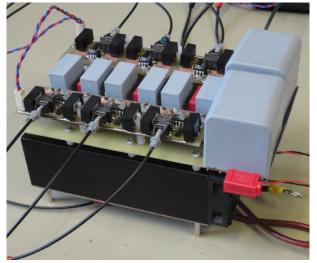

Fig. 9. Developed 14 kVA all SiC AC-DC Grid Connected Converter (GCC) with possibility of short-lived overload up to 28 kVA. TABLE II

| PARAMETERS OF A AC-DC LABORATORY PROTOTYPE |                                            |

|--------------------------------------------|--------------------------------------------|

| Parameter                                  | Film Capacitor                             |

| Rated Power                                | 14 [kVA] / short-lived 28 [kVA]            |

| AC Nominal Voltage                         | 230 [V RMS]                                |

| AC Nominal Current                         | 20.3 [A RMS] /<br>short-lived 40.5 [A RMS] |

| DC Nominal Voltage                         | 700 [V DC]                                 |

| DC Nominal Current                         | 20 [A DC] /<br>short-lived 40 [A DC]       |

| Switching Frequency                        | 40-80 [kHz]                                |

| Line Filter Type                           | LCL                                        |

| Line Filter Parameters                     | For $f_{SW} = 60  [\text{kHz}]$            |

|                                            | $L_{\rm C} = 68 \; [\mu {\rm H}]$          |

|                                            | $C_{\rm F} = 15  [\mu {\rm F}]$            |

|                                            | $L_G = 47 \ [\mu H]$                       |

| DC-link capacitance                        | 180 [µF]                                   |

| DC-link capacitor type                     | Film capacitor Vishay MKP series           |

| Power switch                               | 2 x C2M0080120D                            |

| Freewheeling diode                         | SiC Schottky C4D20120A                     |

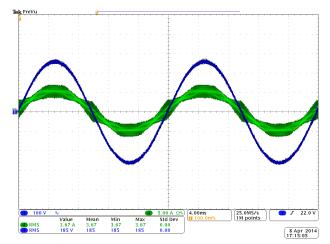

Fig. 10. Start-up of the prototype all SiC AC-DC converter. Current (green) and voltage (blue) waveforms of one phase. Islanding operation (resistive load) with 550 [V] in DC-link,  $f_{\rm SW}{=}40$  kHz.

## V. LABORATORY SETUP

In this section laboratory prototype developed on the basis of methodology presented in sections II and III is introduced. The objective of the design is to achieve high power density and high efficiency for 14 kVA AC-DC converter with possibility of short-lived overload of the converter up to 28 kVA. To achieve design assumptions silicon carbide power MOSFETs from Cree (C2M0080120D) have been selected as switching devices. Two devices are connected in parallel as one switch. As freewheeling diode 10A SiC Schottky diode C4D20120A from Cree has been chosen. Based on performed capacitors analysis film capacitors MKP 1848 from Vishay [30] have been used as a DC-link capacitance. View of designed converter is presented in Fig. 9. Dimensions of the converter are 12.0 x 11.5 x 13.5 cm. Designed operation conditions of the developed 14 kVA GCC are collected in Tab. II. Please note that the prototype is under development. Current and voltage of the prototype which operates in islanding mode with resistive load are presented in Fig. 10.

#### VI. SUMMARY AND CONCLUSIONS

The paper presents short introduction to area of the Multi-Objective Optimization (MOO). Performance indices and optimization parameters used for design of the power electronic converter are described. Methodology of AC-DC Grid Connected Converter (GCC) design according to specified input parameters with local performance indices is proposed. The introduced method is a part of the concept for global optimization of the GCC design parameters. Discrete optimization method which involves evolutionary algorithms for design of three-phase AC-GCC is introduced.

Optimization algorithm is developed as a tool for designer supporting real world industrial solutions. Comparing to approach proposed in [6] procedure takes into account parameters of real components available on the market based on manufacturers' datasheets and no feasibility study is required. Using only mathematical calculations the engineer should be able to observe how changes of one or more parameters will affect the desired system properties and functionalities (design objectives). Operating of the procedure as a web application gives possibility for easy and wide implementation of the proposed methodology. Moreover, required computation speed is provided by the application server. Finally, laboratory prototype of 14 kVA high efficient and compact AC-DC GCC designed according to the methodology is presented. It should be stressed that the converter is under development and only design assumptions and preliminary start-up results are shown. The work will be continued and published.

## ACKNOWLEDGMENT

This work has been supported by the National Science Centre, Poland, based on decision DEC-2012/05/B/ST7/01183 and partially by the European Union in the framework of European Social Fund through the Warsaw University of Technology Development Program, realized by Centre for Advanced Studies.

#### REFERENCES

- Advanced and Intelligent Control in Power Electronics and Drives, Series: Studies in Computational Intelligence, Vol. 531, Editors: T. Orłowska-Kowalska, F. Blaabjerg, J. Rodríguez, Springer International Publishing Switzerland 2014; Chapter 3: Control of Grid Connected Converter (GCC) Under Grid Voltage Disturbances, M. Jasiński, G. Wrona, S. Piasecki, Book Part I, pp 91-142.

- [2] K. Rigbers, "Highly Efficient Inverter Architectures for Three-Phase Grid Connection of Photovoltaic Generators," PhD Thesis, RWTH Aachen University, Germany, pgs. 247, June 2010.

- [3] G. Wrona, M. Jasinski, "AC-DC Converter with Asymmetrical Higher Harmonics Compensation Function in Sustainable AC Grid", Versita, Transaction of Electrical, Control and Communication Engineering, No 2013/2, p. 5-13

- [4] T. Friedli, "Comparative Evaluation of Three-Phase Si and SiC AC-AC Converter Systems," PhD Thesis, ETH Zurich University, Switzerland, pgs. 420, 2010.

- [5] J. Rabkowski, D. Peftitsis, H.P. Nee, "SiC power transistors a new era in power electronics is initiated," IEEE Industrial Electronics Magazine, vol. 6, Issue 2, 2012, pp.17-26.

- [6] J. W. Kolar, J. Biela, S. Waffler, T. Friedli, U. Badstuebner, "Performance trends and limitations of power electronic systems," 6th International Conference on Integrated Power Electronics Systems (CIPS'2010), ISBN: 978-3-8007-3212-8, Germany 2010.

- [7] J. Branke, K. Deb, K. Miettinen, R. Słowiński, "Multiobjective Optimization. Interactive and Evolutionary Approaches," ISSN: 0302-9743, Springer-Verlag Berlin Heidelberg 2008.

- [8] S. Busquets-Monge, G. Soremekun, E. Hefiz, C. Crebier, S. Ragon, D. Boroyevich, Z. Gurdal, M. Arpilliere, D. K. Lindner, "Power Converter Design Optimization," IEEE Industry Applications Magazine, vol. 10, issue 1, pp. 32-38, 2004.

- [9] http://www.mathworks.com/products/matlab/

- [10] http://www.plexim.com/

- [11] http://www.synopsys.com/Systems/Saber/Pages/default.aspx

- [12] http://powersimtech.com/

- [13] http://www.gecko-simulations.com/geckocircuits.html

- [14] http://www.maplesoft.com/

- [15] http://www.adoptech.com/software/OPES.htm

- [16] K. Ejjabraoui, C. Larouci, P. Lefranc, C. Marchand, "Presizing Methodology of DC-DC Converters Using Optimization Under Multiphysic Constraints: Application to a Buck Converter", IEEE Transactions on Industrial Electronics, vol. 59, N. 7, pp.2781-2790, 2012.

- [17] K. Rigbers, S. Schroder, T. Durbaum, M. Wendt, R. W. De Doncker, "Integrated method for optimization of power electronic circuits," IEEE 35th Annual Power Electronics Specialists Conference (PESC 04), vol. 6, pp. 4473-4478, 2004.

- [18] R. T. Marler, J.S. Arora, "Survey of multi-objective optimization methods for engineering", Struct. Multidisc. Optim. 26, pp. 369–395 (2004), Springer-Verlag 2004.

- [19] S. Piasecki, R. Szmurlo, M. Jasinski, "Brief View of Multi-Objective Optimization Approaches Used for Design AC-DC Power Electronics Converters," 14th Intern. Sympos. Topical Problems in the Field of Electrical and Power Engineering, pp. 185-192, Parnu, Estonia, 2014.

- [20] M. Liserre, F. Blaabjerg, S. Hansen, "Design and Control of an LCL-Filter-Based Three-Phase Active Rectifier," IEEE Transactions on Industry Applications, vol. 41, no. 5, pp. 1281-1291, September 2005.

- [21] K. Jalili, S. Bernet, "Design of Filters of LCL Filters of Active-Front-End Two-Level Voltage-Source Converters," IEEE Transactions on Industrial Electronics, vol. 56, no. 5, pp. 1674 - 1689, 2009.

- [22] J. M. Bloemink, T. C. Green, "Reducing passive filter sizes with tuned traps for distribution level power electronics," Power Electronics and Applications (EPE 2011), Proceedings of the 2011-14th European Conference on , vol., no., pp.1-9, Aug. 30 2011-Sept. 1 2011.

- [23] Chas., Proteus, Steinmetz, "On the low of hysteresis", Proc. of the IEEE vol.72, no. 2, pp. 197-221, Feb. 1984.

- [24] M. K. Kazimierczuk, "High-Frequency Magnetic Components," Wiley, 1 edition, October, 2009.

- [25] Rylko, M.S.; Lyons, B.J.; Hayes, J.G.; Egan, M.G., "Revised Magnetics Performance Factors and Experimental Comparison of High-Flux Materials for High-Current DC–DC Inductors," IEEE Transactions on Power Electronics, vol.26, no.8, pp.2112-2126, Aug. 2011.

- [26] http://www.kemet.com

- [27] www.ecicaps.com

- [28] http://www.feas.com

- [29] M. Salcone, J. Bond, "Selecting film bus link capacitors for high performance inverter applications," IEEE International Electric Machines and Drives Conference (IEMDC'09), pp.1692,1699, 3-6 May 2009.

- [30] http://www.vishay.com/capacitors/

- [31] M. Jasinski, "Direct power and torque control of AC/DC/AC converterfed induction motor drives", PhD-thesis, Warsaw University of Technology, Warsaw, Poland, 2005.

- [32] M. H. Bierhoff, F. W. Fuchs, "Power Semiconductor Losses in Voltage Source and Current Source IGBT Converters based on Complete Analytical Derivation," Proceedings of the PESC'04, Aachen, Germany, 2004.

- [33] http://www.cree.com/Power, datasheet of CMF2012D, C2M0080120, C2M0025120, C4D20120A.

- [34] http://www.rohm.com/web/global/, datasheet of SCT2080KE.

- [35] Eckart Zitzler, Marco Laumanns, and Stefan Bleuler, "A Tutorial on Evolutionary Multiobjective Optimization", Conference In Metaheuristics for Multiobjective Optimization, pp. 3-38, 2003.

Szymon Piasecki received the M.Sc.E.E degree in Automatics and Robotics from the Warsaw University of Technology, Faculty of Electrical Engineering, Poland, in 2009. In 2009, he joined the Intelligent Control Group under Professor M. P. Kazmierkowski Since 2010 he is a Ph. D. student in Electrical Engineering Faculty, WUT. His research interests include power converters for renewable energy applications, control of power electronic converters, power grid quality and stability. Since 2013 he is working with problems related to grid's converters design optimization.

Postal address: Warsaw University of Technology, Institute of Control and Industrial Electronics, Koszykowa str. 75, 00-662 Warsaw, Poland. E-mail: szymon.piasecki@ee.pw.edu.pl

**Robert Szmurlo** is an assistant professor at Warsaw University of Technology, Faculty of Electrical Engineering, from where he received his doctoral degree in 2005 in electrical engineering. His major field of study is numerical methods applied to modeling, simulation and optimization in engineering. He has been a visiting scientist to RIKEN Brain Science Institute in Japan in 2005. He is working as an assistant professor and researcher on faculty of Electrical Engineering. He is a member of the ACM. He has been awarded a few times by the Rector of Warsaw University

of Technology for his scientific and educational achievements.

Postal address: Warsaw University of Technology, Institute of Control and Industrial Electronics, Koszykowa str. 75, 00-662 Warsaw, Poland.

E-mail: robert.szmurlo@ee.pw.edu.pl

Marek Jasinski (M'00 SM'12) received the M.Sc.E.E. degree with SEP and IEEE (PS) distinction, and Ph.D. degree in Electrical Engineering from the Institute of Control and Industrial Electronics (ICIE), Warsaw University of Technology (WUT), Warsaw, Poland, in 2000, and in 2005, respectively. Since 2006 he is with the ICIE, WUT as Assistant Professor. His research activity deals with control of power electronics converters for drives and renewable energy sources. He is an author or co-author of more than 60 technical papers. Dr. Jasinski is a IEEE PS Chapters

Coordinator. He was a scholar of Foundation for Polish Science and Center for Advanced Studies of WUT. He received ABB distinction for his Ph.D. dissertation, and SIEMENS Research Award.

Postal address: Warsaw University of Technology, Institute of Control and Industrial Electronics, Koszykowa str. 75, 00-662 Warsaw, Poland. E-mail: mja@isep.pw.edu.pl